ISO/IEC 14575:2000

(Main)Information technology - Microprocessor systems - Heterogeneous InterConnect (HIC) (Low-Cost, Low-Latency Scalable Serial Interconnect for Parallel System Construction)

Information technology - Microprocessor systems - Heterogeneous InterConnect (HIC) (Low-Cost, Low-Latency Scalable Serial Interconnect for Parallel System Construction)

This International Standard applies to physical connectors and cables, electrical properties, and logical protocols for point-to-point serial scalable interconnect, operating at speeds of 10 Mbit/s to 200 Mbit/s and at 1 Gbit/s in copper and optic technologies (as developed in Open Microprocessor Systems Initiative/Heterogeneous InterConnect Project (OMI/HIC)). The object of this International Standard is to enable high-performance, scalable, modular, parallel systems to be constructed with low system integration cost; to support communications systems fabric; to provide a transparent implementation of a range of high-level protocols (communications, e.g. ATM, message passing, shared memory transactions, etc.), and to support links between heterogeneous systems.

Technologies de l'information — Systèmes à microprocesseurs — Interconnexion hétérogène (HIC) (interconnexion en série, à faible coût, faible latence, arborescente pour construction de système parallèle)

General Information

- Status

- Published

- Publication Date

- 19-Jul-2000

- Technical Committee

- ISO/IEC JTC 1/SC 25 - Interconnection of information technology equipment

- Current Stage

- 9093 - International Standard confirmed

- Start Date

- 13-Jul-2018

- Completion Date

- 30-Oct-2025

Overview

ISO/IEC 14575:2000 - Information technology - Microprocessor systems - Heterogeneous InterConnect (HIC) - defines a low-cost, low-latency, scalable serial interconnect for parallel system construction. Developed from the OMI/HIC project and aligned with IEEE Std 1355 (1998), the standard specifies physical connectors and cables, electrical characteristics, and logical protocols for point-to-point serial links operating at 10 Mbit/s to 200 Mbit/s and at 1 Gbit/s in copper and optical technologies. Its objective is to enable modular, high-performance parallel systems and communication fabrics while minimizing system integration cost.

Key topics and technical requirements

- Physical media and connectors: Detailed specifications for copper and fiber optic links, fixed and free connector types, cable recommendations, and PCB/connector footprints (normative annexes cover DS-DE, HS-SE, TS-FO/HS-FO connector specs).

- Electrical properties: Driver/line impedance, signal levels, timing margins, input capacitance and skew parameters for different link classes (DS, HS, TS families).

- Logical protocol layers: Layered model including character, exchange, and packet levels; transparent support for higher-level protocols (ATM, message passing, shared memory transactions).

- Encoding and serialization: Character encoding schemes (for example 8B/12B for HS links) and serialization methods to provide low-latency, reliable serial transmission.

- Routing and packet handling: Packet format, wormhole routing, network topologies, flow control strategies, error detection/recovery and reporting mechanisms.

- Implementation guidance and conformance: Defined implementations, conformance criteria, transaction layer examples (ATM mapping), and informative annexes on switch chips, flow-control calculations, and error handling.

Applications and who uses this standard

ISO/IEC 14575:2000 is intended for engineers and architects building scalable parallel and heterogeneous systems, including:

- System architects designing modular parallel servers and HPC clusters

- Hardware and board-level designers specifying connectors, cables, and PCB footprints

- Network and fabric designers implementing low-latency serial links and switch chips

- Silicon integrators and IP developers implementing serialization, flow control and transaction layers

- Embedded system and telecom designers mapping higher-level protocols (e.g., ATM, message passing) onto a serial fabric

Typical uses include building communication fabrics, interconnecting heterogeneous subsystems, designing switch-based routing fabrics, and creating low-cost, low-latency serial link implementations in copper or fiber.

Related standards

- IEEE Std 1355 (1998) - closely associated and referenced by ISO/IEC 14575:2000

- OMI/HIC project materials - origin and development context for the HIC specifications

Keywords: ISO/IEC 14575, Heterogeneous InterConnect, HIC, serial interconnect, point-to-point, scalable interconnect, DS-SE, DS-DE, HS-SE, TS-FO, packet routing, flow control, wormhole routing, low-latency, parallel system construction.

Frequently Asked Questions

ISO/IEC 14575:2000 is a standard published by the International Organization for Standardization (ISO). Its full title is "Information technology - Microprocessor systems - Heterogeneous InterConnect (HIC) (Low-Cost, Low-Latency Scalable Serial Interconnect for Parallel System Construction)". This standard covers: This International Standard applies to physical connectors and cables, electrical properties, and logical protocols for point-to-point serial scalable interconnect, operating at speeds of 10 Mbit/s to 200 Mbit/s and at 1 Gbit/s in copper and optic technologies (as developed in Open Microprocessor Systems Initiative/Heterogeneous InterConnect Project (OMI/HIC)). The object of this International Standard is to enable high-performance, scalable, modular, parallel systems to be constructed with low system integration cost; to support communications systems fabric; to provide a transparent implementation of a range of high-level protocols (communications, e.g. ATM, message passing, shared memory transactions, etc.), and to support links between heterogeneous systems.

This International Standard applies to physical connectors and cables, electrical properties, and logical protocols for point-to-point serial scalable interconnect, operating at speeds of 10 Mbit/s to 200 Mbit/s and at 1 Gbit/s in copper and optic technologies (as developed in Open Microprocessor Systems Initiative/Heterogeneous InterConnect Project (OMI/HIC)). The object of this International Standard is to enable high-performance, scalable, modular, parallel systems to be constructed with low system integration cost; to support communications systems fabric; to provide a transparent implementation of a range of high-level protocols (communications, e.g. ATM, message passing, shared memory transactions, etc.), and to support links between heterogeneous systems.

ISO/IEC 14575:2000 is classified under the following ICS (International Classification for Standards) categories: 35.160 - Microprocessor systems. The ICS classification helps identify the subject area and facilitates finding related standards.

ISO/IEC 14575:2000 is available in PDF format for immediate download after purchase. The document can be added to your cart and obtained through the secure checkout process. Digital delivery ensures instant access to the complete standard document.

Standards Content (Sample)

INTERNATIONAL ISO/IEC

STANDARD

IEEE

Std 1355

First edition

2000-07

Information Technology –

Microprocessor Systems – Heterogeneous

InterConnect (HIC) (Low-Cost, Low-Latency

Scalable Serial Interconnect for

Parallel System Construction)

Reference number

IEEE Std 1355, 1998 Edition

Abstract: Enabling the construction of high-performance, scalable, modular, parallel systems

with low system integration cost is discussed. Complementary use of physical connectors and

cables, electrical properties, and logical protocols for point-to-point serial scalable

interconnect, operating at speeds of 10 200 Mb/s and at 1 Gb/s in copper and optic

technologies, is described.

Keywords: flow control, encoding schemes, OMI/HIC, packet routing, parallelism, point-to-

point serial scalable interconnect, protocols, routing fabric, serial links, serialization, silicon

integration, switch chip, transaction layer, wormhole routing.

––––––––––––

The Institute of Electrical and Electronics Engineers, Inc.

345 East 47th Street, New York, NY 10017-2394, USA

Copyright © 1998 by the Institute of Electrical and Electronics Engineers, Inc.

All rights reserved. First published in 1998.

ISBN 2-8318-5321-4

No part of this publication may be reproduced in any form, in an electronic retrieval system or otherwise, without

the prior written permission of the publisher.

INTERNATIONAL ISO/IEC

STANDARD

IEEE

Std 1355

First edition

2000-07

Information Technology –

Microprocessor Systems – Heterogeneous

InterConnect (HIC) (Low-Cost, Low-Latency

Scalable Serial Interconnect for

Parallel System Construction)

Sponsor

Bus Architecture Standards Committee

of the IEEE Computer Society

PRICE CODE

XC

For price, see current catalogue

– 2 – ISO/IEC 14575:2000(E)

IEEE Std 1355, 1998 Edition

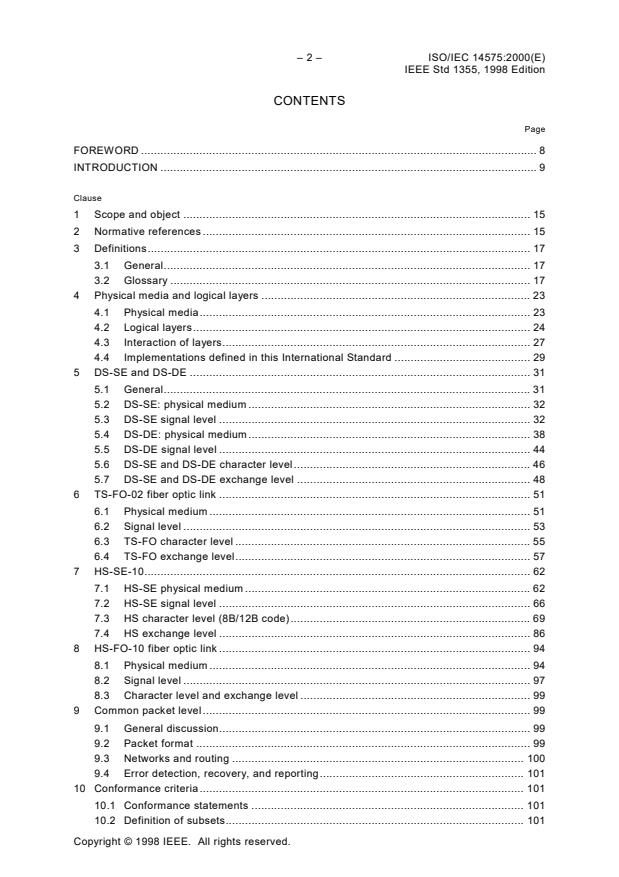

CONTENTS

Page

FOREWORD . 8

INTRODUCTION .9

Clause

1 Scope and object . 15

2 Normative references . 15

3 Definitions. 17

3.1 General. 17

3.2 Glossary . 17

4 Physical media and logical layers . 23

4.1 Physical media. 23

4.2 Logical layers. 24

4.3 Interaction of layers. 27

4.4 Implementations defined in this International Standard . 29

5 DS-SE and DS-DE . 31

5.1 General. 31

5.2 DS-SE: physical medium . 32

5.3 DS-SE signal level . 32

5.4 DS-DE: physical medium. 38

5.5 DS-DE signal level . 44

5.6 DS-SE and DS-DE character level. 46

5.7 DS-SE and DS-DE exchange level . 48

6 TS-FO-02 fiber optic link . 51

6.1 Physical medium . 51

6.2 Signal level . 53

6.3 TS-FO character level . 55

6.4 TS-FO exchange level. 57

7 HS-SE-10.62

7.1 HS-SE physical medium . 62

7.2 HS-SE signal level . 66

7.3 HS character level (8B/12B code). 69

7.4 HS exchange level . 86

8 HS-FO-10 fiber optic link . 94

8.1 Physical medium . 94

8.2 Signal level . 97

8.3 Character level and exchange level . 99

9 Common packet level. 99

9.1 General discussion. 99

9.2 Packet format . 99

9.3 Networks and routing . 100

9.4 Error detection, recovery, and reporting. 101

10 Conformance criteria. 101

10.1 Conformance statements . 101

10.2 Definition of subsets. 101

Copyright © 1998 IEEE. All rights reserved.

IEEE Std 1355, 1998 Edition

Annex A (normative) DS-DE connector specification . 103

Annex B (normative) HS-SE connector specification . 110

Annex C (normative) TS-FO and HS-FO connector specifications . 116

Annex D (informative) Rationale . 128

Annex E (informative) Switch chips, switches, and fabrics . 132

Annex F (informative) Use of the transaction layer – Asynchronous transfer mode (ATM)

example . 134

Annex G (informative) Error handling . 145

Annex H (informative) Flow control calculations . 146

Annex I (informative) Synchronized channel communications . 149

Annex J (informative) Example DS-SE driver circuit . 152

Annex K (informative) DS-DE optional power supply recommendation . 154

Annex L (informative) DS-DE fixed connector PCB recommendation . 155

Annex M (informative) DS-DE cable (10 core) recommendation. 156

Annex N (informative) DS-DE multiway connector housing recommendation. 157

Annex O (informative) HS-SE fixed connector PCB recommendation. 158

Annex P (informative) HS-SE cable recommendation . 159

Annex Q (informative) HS-SE connector multiway housing recommendation. 160

Annex R (informative) TS/HS-FO connector PCB and front panel cut-out recommendation . 161

Annex S (informative) TS/HS-FO fiber cable recommendation. 162

Figure 1 – Protocol stack between nodes . 23

Figure 2 – Exchange layer . 26

Figure 3 – Protocol stack diagram showing interaction of layers . 28

Figure 4 – Defined implementation of physical and logical layers. 30

Figure 5 – DS-SE link signal propagation . 33

Figure 6 – DS-SE timing reference model . 35

Figure 7 – DS-SE link timings . 36

Figure 8 – DS-SE link signal encoding . 37

Figure 9 – DS-DE cable assembly twist example. 40

Figure 10 – DE-DE extension adapter . 40

Figure 11 – DS-DE fixed connector external view. 41

Figure 12 – Multiple power connectors . 43

Figure 13 – DS-SE/DS character encoding. 46

Figure 14 – DS-SE/DS-DE parity coverage. 47

Figure 15 – DS link states. 49

Figure 16 – DS link start-up and reset. 50

Figure 17 – TS-FO cable fibers/plugs wiring. 52

Figure 18 – TS-FO extension adapter . 52

Figure 19 – TS-FO fixed adaptor, external view and ferrule allocation. 53

Figure 20 – TS-FO reference list. 54

Figure 21 – TS-FO link states . 58

Figure 22 – TS link start-up and reset . 59

Copyright © 1998 IEEE. All rights reserved.

– 4 – ISO/IEC 14575:2000(E)

IEEE Std 1355, 1998 Edition

Figure 23 – TS-FO packet encoding. 61

Figure 24 – Single braid and double braid link cables . 64

Figure 25 – HS-SE cable pins/connectors wiring . 65

Figure 26 – HS-SE extension adapter . 65

Figure 27 – HS-SE fixed connector external view . 65

Figure 28 – Input and output buffer electrical model . 67

Figure 29 – Exchange level interconnection between two nodes . 87

Figure 30 – Transmitter state machine controller-start-up. 88

Figure 31 – Transmitter state machine controller-functional. 89

Figure 32 – Transmitter state machine controller-shutdown. 89

Figure 33 – Receiver state machine controller. 90

Figure 34 – Exchange for start-up, functional and shutdown. 91

Figure 35 – Exchange for bidirectional start-up . 92

Figure 36 – HS-FO cable fibers/plugs wiring . 95

Figure 37 – HS-FO extension adapter . 96

Figure 38 – HS-FO fixed adapter, external view and ferrule allocation . 96

Figure 39 – HS-FO reference link . 98

Figure A.1 – DS-DE fixed connector front view. 105

Figure A.2 – DS-DE fixed connector side view. 106

Figure A.3 – DS-DE fixed connector top view . 106

Figure A.4 – DS-DE connector latch. 107

Figure A.5 – DS-DE free connector front view . 108

Figure A.6 – DS-DE free connector side view. 109

Figure A.7 – DS-DE free connector contact. 109

Figure B.1 – HS-SE free connector front view . 112

Figure B.2 – HS-SE free connector side view . 112

Figure B.3 – HS-SE fixed connector front view . 113

Figure B.4 – HS-SE fixed connector side view. 113

Figure B.5 – HS-SE connector link . 114

Figure B.6 – HS-SE contact interface dimensions . 115

Figure C.1 – TS-FO/HS-FO link free connector . 126

Figure C.2 – TS-FO/HS-FO link fixed connector. 127

Figure F.1 – ATM network. 134

Figure F.2 – ATM layers . 136

Figure F.3 – Virtual channels and virtual paths. 137

Figure F.4 – Example of virtual path and virtual channel switching. 138

Figure F.5 – ATM cell header. 139

Figure F.6 – Mapping reference model. 140

Figure H.1 – Theoretical maximum transmission length calculation . 147

Figure H.2 – Distance versus buffer size for DS and TS links . 147

Copyright © 1998 IEEE. All rights reserved.

IEEE Std 1355, 1998 Edition

Figure H.3 – Distance versus buffer size for HS-SE links . 148

Figure J.1 – DS-SE pad equivalent circuit . 153

Figure J.2 – Simulation input waveforms . 153

Figure K.1 – Optional power supply circuit. 154

Figure L.1 – DS-DE fixed connector PCB layout . 155

Figure M.1 – Recommended DS-DE link cable cross-section. 156

Figure N.1 – DS-DE connector multiway housing. 157

Figure N.2 – DS-DE (multiway) front panel cut-out . 157

Figure P.1 – Recommended HS-SE link shielded cable cross-section. 159

Figure O.1 – Recommended HS-SE fixed connector PCB layout . 158

Figure Q.1 – HS-SE multiway housing. 160

Figure Q.2 – HS-SE (multiway) front panel cut out . 160

Figure R.1 – TS/HS-FO fixed connector PCB footprint. 161

Figure R.2 – TS/HS-FO fixed connector front panel cut-out . 161

Figure S.1 – Example of TS/HS-FO fiber cable structure . 162

Table 1 – Identification format for technologies . 30

Table 2 – Defined implementations . 31

Table 3 – Driver to line impedance matching table . 34

Table 4 – DS-SE input capacitance. 34

Table 5 – DS-SE timing and swings . 35

Table 6 – DS-SE output skew parameters . 37

Table 7 – Identification of multiple link interfaces . 38

Table 8 – DS-DE cable color code . 38

Table 9 – Electrical and mechanical characteristics and safety certification of DS-DE cable. 39

Table 10 – DS-DE link cable conductors/connectors wiring . 40

Table 11 – Pin allocation of DS-DE connector . 41

Table 12 – DS-DE connector modularity specifications. 41

Table 13 – DS-DE environmental constraints . 42

Table 14 – Optional power supply . 42

Table 15 – Optional power supply load. 42

Table 16 – Optional power supply protective device . 43

Table 17 – DS-DE signal levels. 44

Table 18 – DS-DE correspondence . 45

Table 19 – Attribution of attenuation budget . 45

Table 20 – Attribution of skew budget . 45

Table 21 – Terminator character codings . 47

Table 22 – Link control character codings . 47

Table 23 – Summary of main optical characteristics of TS-FO fibers . 51

Table 24 – TS-FO connector modularity specifications . 52

Table 25 – TS-FO signal allocation . 53

Table 26 – TS-FO environmental constraints. 53

Table 27 – TS-FO recommended transceiver characteristics . 54

Copyright © 1998 IEEE. All rights reserved.

– 6 – ISO/IEC 14575:2000(E)

IEEE Std 1355, 1998 Edition

Table 28 – TS-FO link performance specification . 55

Table 29 – Symbols allocated for character coding of data values . 56

Table 30 – Symbols for control characters . 56

Table 31 – Coding of control characters. 57

Table 32 – Coding of INIT. 57

Table 33 – HS-SE-10 links general characteristics . 62

Table 34 – PCB track characteristics . 62

Table 35 – Physical characteristics of a single coaxial cable . 63

Table 36 – Electrical characteristics of a single coaxial cable . 63

Table 37 – Mechanical performance and safety certification of link cables. 64

Table 38 – Pin allocation of HS-SE connector . 66

Table 39 – HS-SE environmental constraints . 66

Table 40 – HS-SE environmental constraints . 66

Table 41 – Operating rates for HS-SE-10 links . 66

Table 42 – Attribution of attenuation budget . 68

Table 43 – Driver side line logic levels for V = 3.3 V (nominal). 68

DD

Table 44 – Driver side line logic levels for V = 5.0 V (nominal). 68

DD

Table 45 – Driver side line swing when ac coupled into 50 Ω termination . 68

Table 46 – Receiver electrical characteristics. 69

Table 47 – Data characters. 72

Table 48 – Control characters. 83

Table 49 – Reserved L_chars for exchange level functions . 87

Table 50 – Time-out values. 92

Table 51 – Summary of main optical characteristics of HS-FO fibers . 95

Table 52 – THS-FO connector modularity specifications. 95

Table 53 – HS-FO signal allocation. 96

Table 54 – HS-FO environmental constraints . 96

Table 55 – HS-FO recommended transceiver characteristics for multimode fiber. 97

Table 56 – HS-FO recommended transceiver characteristics for single mode fiber . 97

Table 57 – HS-FO link performance specification. 98

Table 58 – End_of_packet markers. 100

Table 59 – Codes for EOP markers. 100

Table 60 – Conformance identifications for connectors. 101

Table 61 – Conformance identifications for link cables . 101

Table 62 – Conformance identifications for link cable assemblies. 102

Table 63 – Common identifications for link interfaces. 102

Table A.1 – DS-DE connector requirements . 103

Table B.1 – HS-SE connector requirements . 110

Copyright © 1998 IEEE. All rights reserved.

IEEE Std 1355, 1998 Edition

Table C.1 – TS-FO and HS-FO (multimode) connector requirements. 116

Table C.2 – Performance and environmental specification for TS-FO and HS-FO

(multimode) connector . 119

Table C.3 – HS-FO (single-mode) connector requirements. 121

Table C.4 – Performance and environmental specification for HS-FO

(single-mode) connector . 124

Table C.5 – Color coding of TS/HS-FO connectors. 127

Table J.1 – Parameter spread for DS-SE link driver . 152

Table L.1 – PCB details for DS-DE connector attachment . 155

Table M.1 – Recommended DS-DE link cable specification . 156

Table P.1 – Recommended HS-SE cable specifications . 159

Copyright © 1998 IEEE. All rights reserved.

– 8 – ISO/IEC 14575:2000(E)

IEEE Std 1355, 1998 Edition

INFORMATION TECHNOLOGY – MICROPROCESSOR SYSTEMS –

HETEROGENEOUS INTERCONNECT (HIC)

(LOW-COST, LOW-LATENCY SCALABLE SERIAL INTERCONNECT

FOR PARALLEL SYSTEM CONSTRUCTION)

FOREWORD

1) ISO (the International Organization for Standardization) and IEC (the International Electrotechnical Commission)

form the specialized system for worldwide standardization. National bodies that are members of ISO or IEC

participate in the development of International Standards through technical committees established by the

respective organization to deal with particular fields of technical activity. ISO and IEC technical committees

collaborate in fields of mutual interest. Other international organizations, governmental and non-governmental,

in liaison with ISO and IEC, also take part in the work.

2) In the field of information technology, ISO and IEC have established a joint technical committee, ISO/IEC JTC1.

Draft International Standards adopted by the joint technical committee are circulated to national bodies for

voting. Publication as an International Standard requires approval by at least 75 % of the national bodies

casting a vote.

3) Attention is drawn to the possibility that some of the elements of this International Standard may be the subject

of patent rights. ISO and IEC shall not be held responsible for identifying any or all such patent rights.

International Standard ISO/IEC 14575 was prepared by subcommittee 26: Microprocessor

systems, of ISO/IEC joint technical committee 1: Information technology.

International Standards are drafted in accordance with ISO/IEC Directives, Part 3.

Annexes A, B and C form an integral part of this standard.

Annexes D, E, F, G, H, I, J, K, L, M, N, O, P, Q, R and S are for information only.

International Electrotechnical Commission • 3, rue de Varembé, PO Box 131,

CH-1211-Geneva 20, Switzerland Telephone: +41 22 919 0211

Telefax: +41 22 919 0300 e-mail: inmail@iec.ch

URL: http://www.iec.ch

Copyright © 1998 IEEE. All rights reserved.

IEEE Std 1355, 1998 Edition

INTRODUCTION

(This introduction is not a normative part of ISO/IEC 14575:2000, but is included for information

only.)

The construction of high-performance systems with parallel communications, parallel

processing, and/or parallel I/O demands a fast, low-cost, low-latency interconnect. It must be

fast and low-latency, otherwise it will be the limiting factor in system performance; and it must

be low-cost, or it will dominate the system cost. It must also scale well in both performance and

cost relative to the system size, otherwise highly parallel systems will be limited in performance

or too expensive. Existing standards do not meet these criteria, because they are designed for

communication over long distances (which incurs high costs), or because they aim at the

extreme of currently achievable performance (which again increases costs), or because they

are based on a restricted model such as a bus, which limits overall performance and

scalability. A detailed rationale for this standard is given in annex D.

This standard has been developed to complement recent technical developments of highly

integrated, low-power interconnect technology implemented in high-volume commodity VLSI

processes, and to exploit the simplifications in encodings and protocols resulting from the use

of relatively reliable media over relatively short distances. Aspects of the baseline for this

standard have their origins in work on parallel systems, which has taken place in a number of

ESPRIT projects. In particular, the routing strategy was established in the PUMA project, and

the DS-Links were developed partially in the GP MIMD project. Work at interconnect for high-

performance mainframe computers at Bull led to the development of the gigabit link technology

implemented in Bi-CMOS and CMOS processes. More recently, these developments, together

with corresponding optical technology, have been brought together in the OMI/HIC Project

(Open Microprocessor Systems Initiative – High Performance Heterogeneous Interconnect –

ESPRIT 7252).

Attention is called to the possibility that implementation of this standard may require use of

subject matter covered by patent rights. By publication of this standard, no position is taken

with respect to the existence or validity of any patent rights in connection therewith. The IEEE

shall not be responsible for identifying all patents for which a license may be required by an

IEEE standard or for conducting inquiries into the legal validity or scope of those patents that

are brought to its attention.

The patent holder has, however, filed a statement of assurance that it will grant a license under

these rights without compensation or under reasonable rates and nondiscriminatory,

reasonable terms and conditions to all applicants desiring to obtain such a license. The IEEE

makes no representation as to the reasonableness of rates and/or terms and conditions of the

license agreement offered by the patent holder. Contact information may be obtained from the

IEEE Standards Department.

Copyright © 1998 IEEE. All rights reserved.

– 10 – ISO/IEC 14575:2000(E)

IEEE Std 1355, 1998 Edition

This standard has been developed with the efforts of many volunteers. The following is a list of

those who attended Working Group meetings while the draft and final standard documents

were compiled:

Colin Whitby-Strevens, Chair

Roland Marbot, Co-Chair

Andrew Coffer, Editor

Harry Andreas Howard Gurney Michel Monchant

Noriaki Arikawa Claes-Goran Gustavsson Jonathan Morris

Dan Ater Stefan Haas Ken Naumann

Ton Balhaar Brian Henderson Joe Norris

Edmund H. Baulsir Geoffrey Hilton Mats Olstedt

Harrison Beasley Roger Hinsdale Joar Martin Ostby

Ralf Bokamper Geir Horn Sylvain Paineau

Thierry Brizard Shinichi Iwano Elwood Parsons

Joe Brown Ed Jacques David Robak

Richard Carlson Bjorn Johnsbraten Eivind Rongved

Stephen J. Cecil Anatol Kaganovich Pino Rosario

Jean Jacques Chaput Thomas Kessler Jouko Saarinen

Michael Christ Jangkyung Kim Yasuo Sasaki

Chip Coffin Terry Kingham Michael Scott

Stefan De Troch Bill Kirk Tor Skeie

Jean-Merri De Vanssay Matthew Kirwan Nobuaki Sugiura

Gerry Desmody Ernst Kristiansen Peter Thompson

Ian Dobson Alain Lagarde Joe Trainor

Jean Jacques Dumont Falk Langhammer Toine van Laarhoven

Mike Foster Craig Lund Rob Volgers

David Franklin Calogero Mantellina Richard Wagner

Bob Gannon Brian Martin Paul Walker

Stein Gjessing Kristian Martinson Alan Welzel

Oystein Gran Larsen Paolo Melloni David L. Wright

Contributions have also been received from:

Yogindra Abhyankar Bruno Houssay James Wolffe

Dave Cormie Reza Nezamzadeh Bin Wu

Copyright © 1998 IEEE. All rights reserved.

IEEE Std 1355, 1998 Edition

The following persons were on the balloting committee:

Ghassan Abbas Stefan Haas Elwood Parsons

Malcom Airst Bruno Houssay Mohan Patnaik Lalit

Harry Andreas Phillip Hughes Mira Pauker

Keith Anthony Shinichi Iwano Patrick Plancke

James Barnette David James Mike Polehn

Edmund Baulsir Daniel Jochym Brian Ramelson

Harrison Beasley Sherry Johnson Douglas Rawson-Harris

Christos Bezirtzoglou Sun-Moo Kang David Robak

Harold Blatter Yoshihisa Kawamura Fred Rosenberger

Timothy Boggess Stephen Kempainen Yasuo Sasaki

Ralf Bokamper Jangkyunk Kim Frederick Sauer

John Brightwell Jan Kindervater Rudolf Schubert

Charles Brill Hans Peter Kraus Shreyas Shah

Chris Brown Ernst Kristiansen Tahir Sheikh

Joe Brown Thomas Kulesza Tor Skeie

Trevor Carden Falk Langhammer Paul Slootweg

Richard Carlson Conrad Laurvick Nobuaki Sugiura

Yoon Chang Michael Lazar Michael Teener

Andy Cheese Udo Lechner Michael Thompson

C. Chen Rollins Linser Peter Thompson

Michael Christ Gary Manchester Michael Timperman

Andrew Cofler Roland Marbot Dirk Van de Lagemaat

Patrick Courtney Joseph Marshall Richard Wagner

Robert Crowder Brian Martin Paul Walker

Robert Dahlgren Wolfgang Meier Thomas Wegmann

Martin Davis Michel Maillet Alan Wetzel

Dante Del Corso Michael Miskin Colin Whitby-Strevens

Ian Dobson Yoshiki Mitani Jeffrey Wills

Jean-Jacques Dumont Klaus-Dieter Mueller James Wolffe

Sourav Dutta Michael Munroe Anthony Wood

Wayne Fischer J. Nicoud J. Robert Wood

Gordon Force Joe Norris Bill Woodruff

Bob Gannon Daniel O'Connor David Wright

Stein Gjessing Katsuyuki Okada Bin Wu

Chuck Grant Fred Orlando Oren Yuen

Peter Gutgarts Granville Ott Janusz Zalewski

Copyright © 1998 IEEE. All rights reserved.

– 12 – ISO/IEC 14575:2000(E)

IEEE Std 1355, 1998 Edition

When the IEEE Standards Board approved this standard on September 21, 1995, it had the

following membership:

E. G. "Al" Kiener, Chair Donald C. Loughry, Vice Chair

Andrew G. Salem, Secretary

Gilles A. Baril Jim Isaak Marco W. Migliaro

Clyde R. Camp Ben C. Johnson Mary Lou Padgett

Joseph A. Cannatelli Sonny Kasturi John W. Pope

Stephen L. Diamond Lorraine C. Kevra Arthur K. Reilly

Harold E. Epstein Ivor N. Knight Gary S. Robinson

Donald C. Fleckenstein Joseph L. Koepfinger* Ingo Rüsch

Jay Forster* D. N. "Jim" Logothetis Chee Kiow Tan

Donald N. Heirman L. Bruce McClung Leonard L. Tripp

Richard J. Holleman Howard L. Wolfman

* Member Emeritus

Also included are the following nonvoting IEEE Standards Board liaisons:

Satish K. Aggarwal

Richard B. Engelman

Robert E. Hebner

Chester C. Taylor

Lisa S. Young

IEEE Standards Project Editor

IEEE Std 1355-1995 was approved by the American National Standards

Institute on 8 April 1996.

Copyright © 1998 IEEE. All rights reserved.

IEEE Std 1355, 1998 Edition

IEEE Standards documents are developed within the Technical Committees of the IEEE

Societies and the Standards Coordinating Committees of the IEEE Standards Board. Members

of the committees serve voluntarily and without compensation. They are not necessarily

members of the Institute. The standards developed within IEEE represent a consensus of the

broad expertise on the subject within the Institute as well as those activities outside of IEEE

that have expressed an interest in participating in the development of the standard.

Use of an IEEE Standard is wholly voluntary. The existence of an IEEE Standard does not

imply that there are no other ways to produce, test, measure, purchase, market, or provide

other goods and services related to the scope of the IEEE Standard. Furthermore, the

viewpoint expressed at the time a standard is approved and issued is subject to change

brought about through developments in the state of the art and comments received from users

of the standard. Every IEEE Standard is subjected to review at least every five years for

revision or reaffirmation. When a document is more than five years old and has not been

reaffirmed, it is reasonable to conclude that its contents, although still of some value, do not

wholly reflect the present state of the art. Users are cautioned to check to determine that they

have the latest edition of any IEEE Standard.

Comments for revision of IEEE Standards are welcome from any interested party, regardless of

membership affiliation with IEEE. Suggestions for changes in documents should be in the form

of a proposed change of text, together with appropriate supporting comments.

Interpretations: Occasionally questions may arise regarding the meaning of portions of

standards as they relate to specific applications. When the need for interpretations is brought

to the attention of IEEE, the Institute will initiate action to prepare appropriate responses. Since

IEEE Standards represent a consensus of all concerned interests, it is important to ensure that

any interpretation has also received the concurrence of a balance of interests. For this reason

IEEE and the members of its technical committees are not able to provide an instant response

to interpretation requests except in those cases where the matter has previously received

formal consideration.

Comments on standards and requests for interpretations should be addressed to:

Secretary, IEEE Standards Board

445 Hoes Lane

P.O. Box 1331

Piscataway, NJ 08855-1331

USA

Note: Attention is called to the possibility that implementation of this standard may

require use of subject matter covered by patent rights. By publication of this

standard, no position is taken with respect to the existence or validity of any patent

rights in connection therewith. The IEEE shall not be responsible for identifying all

patents for which a license may be required by an IEEE standard or for conducting

inquiries into the legal validity or scope of those patents that are brought to its

attention.

Authorization to photocopy portions of any individual standard for internal or personal use is

granted by the Institute of Electrical and Electronics Engineers, Inc., provided that the

appropriate fee is paid to Copyright Clearance Center. To arrange for payment of licensing fee,

please contact Copyright Clearance Center, Customer Service, 222 Rosewood Drive, Danvers,

MA 01923 USA; (508) 750-8400. Permission to photocopy portions of any individual standard

for educational classroom use can also be obtained through the Copyright Clearance Center.

Copyright © 1998 IEEE. All rights reserved.

– 14 – ISO/IEC 14575:2000(E)

IEEE Std 1355, 1998 Edition

Copyright © 1998 IEEE. All rights reserved.

IEEE Std 1355, 1998 Edition

INFORMATION TECHNOLOGY – MICROPROCESSOR SYSTEMS –

HETEROGENEOUS INTERCONNECT (HIC)

(LOW-COST, LOW-LATENCY SCALABLE SERIAL INTERCONNECT

FOR PARALLEL SYSTEM CONSTRUCTION)

1 Scope and object

This International Standard applies to physical connectors and cables, electrical properties,

and logical protocols for point-to-point serial scalable interconnect, operating at speeds of

10 Mbit/s to 200 Mbit/s and at 1 Gbit/s in copper and optic technologies (as developed in Open

Microprocessor Systems Initiative/Heterogeneous InterConnect Project (OMI/HIC)).

The object of this International Standard is to enable high-performance, scalable, modular,

parallel systems to be constructed with low system integration cost; to support communications

systems fabric; to provide a transparent implementation of a range of high-level protocols

(communications, e.g. ATM, message passing, shared memory transactions, etc.), and to

support links between heterogeneous systems.

2 Normative references

The following normative documents contain provisions which, through reference in this text,

constitute provisions of this International Standard. For dated references, subsequent

amendments to, or revisions of, any of these publications do not apply. However, parties to

agreements based on this International Standard are encouraged to investigate the possibility

of applying the most recent editions of the normative documents indicated below. For undated

references, the latest edition of the normative document referred to applies. Members of ISO

and IEC maintain registers of currently valid International Standards.

CISPR 22, Information technology equipment – Radio disturbance characteristics – Limits of

methods of measurement

IEC 60352-5:1995, Solderless connections – Part 5: Solderless press-in connections – General

requirements, test methods and practical guidance

IEC 60512-2:1985, Electromechanical components for electronic equipment; basic testing

procedures and measuring methods – Part 2: General examination, electrical continuity and

contact resistance tests, insulation tests and voltage stress tests

IEC 60512-3:1976, Electromechanical components for electronic equipment; basic testing

procedures and measuring methods – Part 3: Current-carrying capacity tests

IEC 60512-4:1976, Electromechanical components for electronic equipment; basic testing

procedures and measuring methods – Part 4: Dynamic stress tests

IEC 60512-5:1992, Electromechanical components for electronic equipment; basic testing

procedures and measuring methods – Part 5: Impact tests (free components), static load tests

(fixed components), endurance tests and overload tests

IEC 60512-6:1984, Electromechanical components for electronic equipment; basic testing

procedures and measuring methods – Part 6: Climatic tests and soldering tests

IEC 60512-7:1993, Electromechanical components for electronic equipment; basic testing

procedures and measuring methods – Part 7: Mechanical operating tests and s

...

Questions, Comments and Discussion

Ask us and Technical Secretary will try to provide an answer. You can facilitate discussion about the standard in here.

Loading comments...